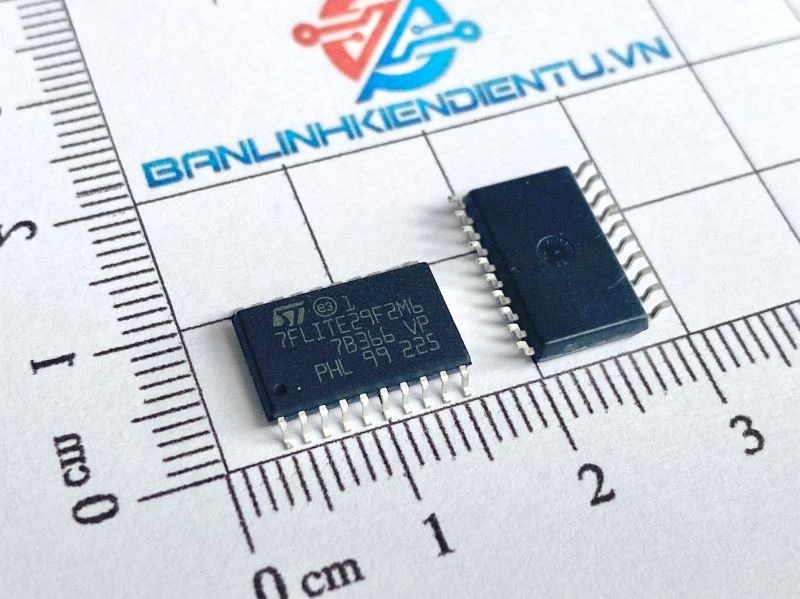

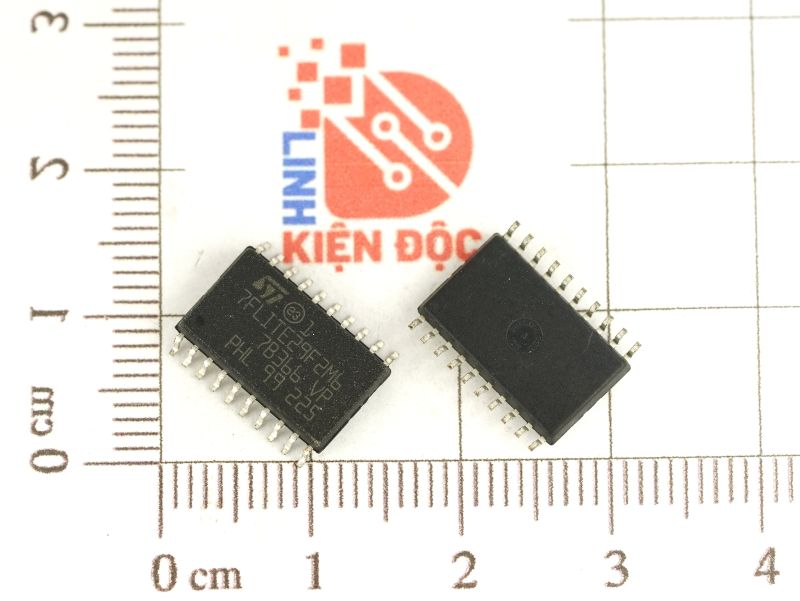

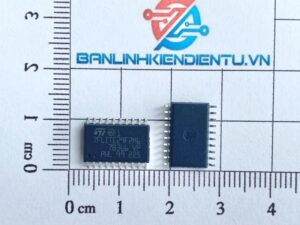

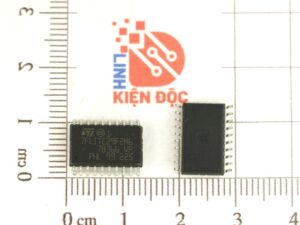

ST7FLITE29F2M6 Vi điều khiển 8 BIT SOP-20

50,000₫

Kinh doanh 1: 0333595662

Kinh doanh 2: 0973549046

(Giờ làm việc: 8h đến 18h từ T2-T7 )

Chú ý: Chỉ gửi đơn hàng tối thiểu 50.000 vnđ. Đơn hàng chưa bao gồm phí vận chuyển.

Giới thiệu 7FLITE29F2M6

ST7LITE29F2 được gọi là ST7LITE2. ST7LITE2 là thành viên của họ vi điều khiển ST7.

Tất cả các thiết bị ST7 đều dựa trên lõi 8 bit tiêu chuẩn công nghiệp chung, có bộ lệnh nâng cao. ST7LITE2 có bộ nhớ FLASH với khả năng Lập trình trong mạch (ICP) và Lập trình trong ứng dụng (IAP) từng byte. Dưới sự điều khiển của phần mềm, thiết bị ST7LITE2 có thể được đặt ở chế độ WAIT, SLOW hoặc HALT, giúp giảm mức tiêu thụ điện năng khi ứng dụng ở trạng thái nhàn rỗi hoặc chờ. Bộ lệnh nâng cao và chế độ định địa chỉ của ST7 cung cấp cả sức mạnh và tính linh hoạt cho các nhà phát triển phần mềm, cho phép thiết kế mã ứng dụng hiệu quả cao và nhỏ gọn.

Ngoài quản lý dữ liệu 8 bit tiêu chuẩn, tất cả các vi điều khiển ST7 đều có chế độ thao tác bit thực, phép nhân không dấu 8×8 và chế độ định địa chỉ gián tiếp.

Đặc tính kĩ thuật 7FLITE29F2M6

■ Bộ nhớ

– Bộ nhớ Flash chương trình điện áp đơn 8 Kbyte với chức năng bảo vệ Đọc ra

– Lập trình trong mạch và lập trình trong ứng dụng (ICP và IAP)

– Đảm bảo 10K chu kỳ ghi/xóa

– Lưu trữ dữ liệu: 20 năm ở 55 °C

– Phạm vi nhiệt độ: -40°C đến 105°C

– 384 byte RAM.

■ Quản lý đồng hồ, đặt lại và cung cấp

– Hệ thống đặt lại nâng cao

– Giám sát điện áp thấp (LVD) nâng cao cho nguồn cung cấp chính và một máy dò điện áp phụ (AVD) có khả năng ngắt để thực hiện các quy trình tắt nguồn an toàn

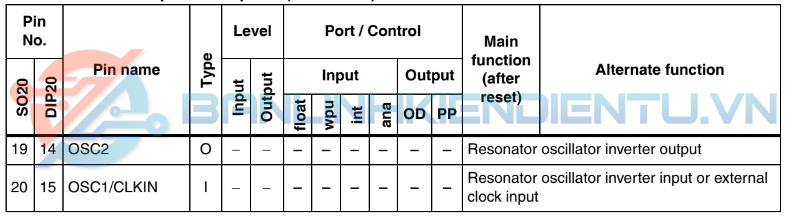

– Nguồn đồng hồ: bộ dao động RC 1% bên trong, bộ cộng hưởng tinh thể/gốm hoặc đồng hồ bên ngoài

– Đồng hồ đầu vào 32 MHz bên trong cho bộ hẹn giờ tự động tải lại

– PLL x4 hoặc x8 tùy chọn cho đồng hồ bên trong 4 hoặc 8 MHz

– Năm chế độ tiết kiệm điện: Dừng, Dừng chủ động, Chờ và Chậm, Tự động đánh thức từ Dừng.

■ Cổng I/O

– Tối đa 15 đường I/O song hướng đa chức năng

– 7 đầu ra high sink.

■ 4 bộ hẹn giờ

– Bộ hẹn giờ giám sát có thể cấu hình

– Hai bộ hẹn giờ Lite 8 bit với bộ chia trước

– 1 cơ sở thời gian thực và 1 bộ thu thập đầu vào

– Một bộ hẹn giờ tự động tải lại 12 bit với 4 đầu ra PWM, chức năng thu thập đầu vào và so sánh đầu ra.

■ 1 giao diện truyền thông

– Giao diện nối tiếp đồng bộ SPI.

■ Quản lý ngắt

– 10 vectơ ngắt cộng với TRAP và RESET

– 15 đường ngắt ngoài (trên 4 vectơ).

■ Bộ chuyển đổi A/D

– 7 kênh đầu vào

– Bộ khuếch đại hoạt động có độ lợi cố định

– Độ phân giải 13 bit cho 0 đến 430 mV (@ 5 V VDD)

– Độ phân giải 10 bit cho 430 mV đến 5 V (@ 5 V VDD).

■ Bộ lệnh

– Thao tác dữ liệu 8 bit

– 63 lệnh cơ bản với chức năng phát hiện mã lệnh bất hợp pháp

– 17 chế độ định địa chỉ chính

– 8 x 8 lệnh nhân không dấu.

■ Công cụ phát triển

– Gói phát triển phần cứng/phần mềm đầy đủ

– DM (mô-đun gỡ lỗi)

Sơ đồ khối

Sơ đồ chân

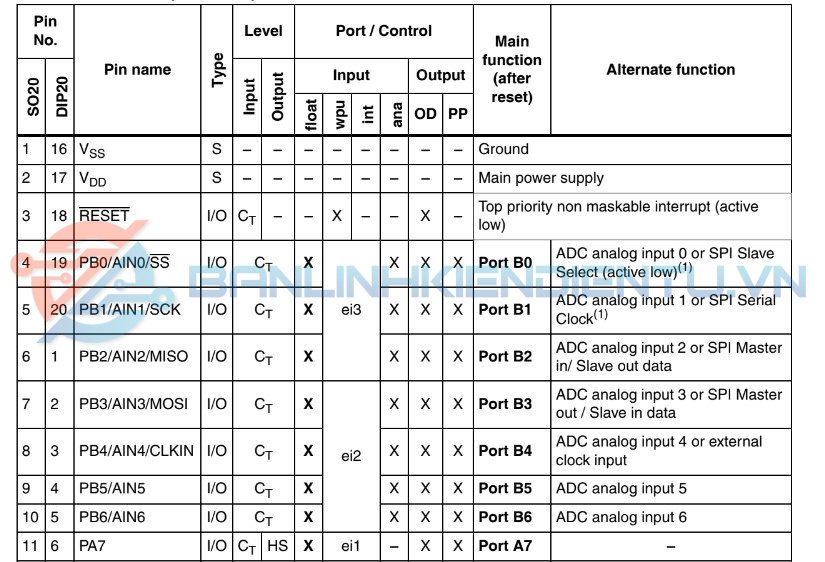

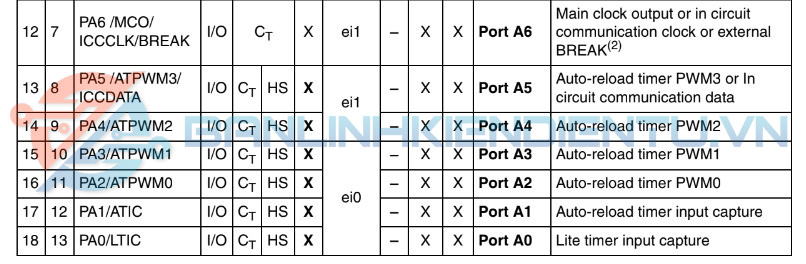

Bảng mô tả chân

Bộ nhớ dữ liệu

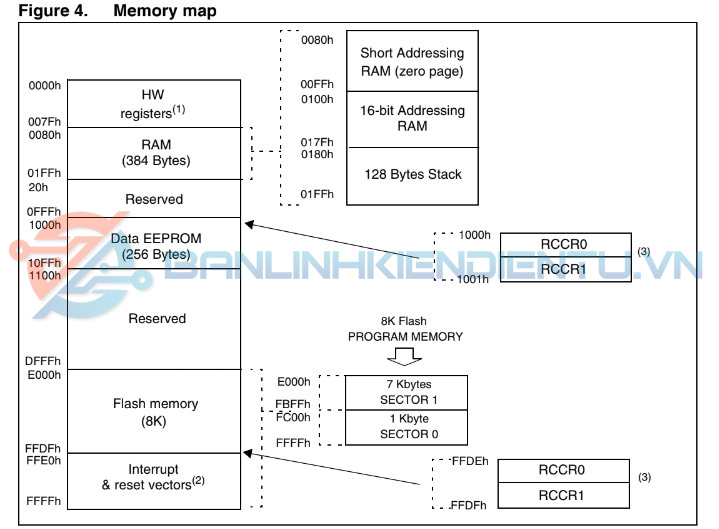

Như thể hiện trong hình, MCU có khả năng định địa chỉ 64K byte bộ nhớ và thanh ghi I/O. Các vị trí bộ nhớ khả dụng bao gồm 128 byte vị trí thanh ghi, 384 byte RAM, 256 byte EEPROM dữ liệu và 8 Kbyte bộ nhớ chương trình người dùng. Không gian RAM bao gồm tối đa 128 byte cho ngăn xếp từ 180h đến 1FFh. Các byte địa chỉ cao nhất chứa các vectơ ngắt và đặt lại của người dùng. Bộ nhớ Flash chứa hai sector (xem Hình 4) được ánh xạ ở phần trên của không gian định địa chỉ ST7 để các vectơ ngắt và đặt lại nằm trong Sector 0 (F000h-FFFFh).

CPU

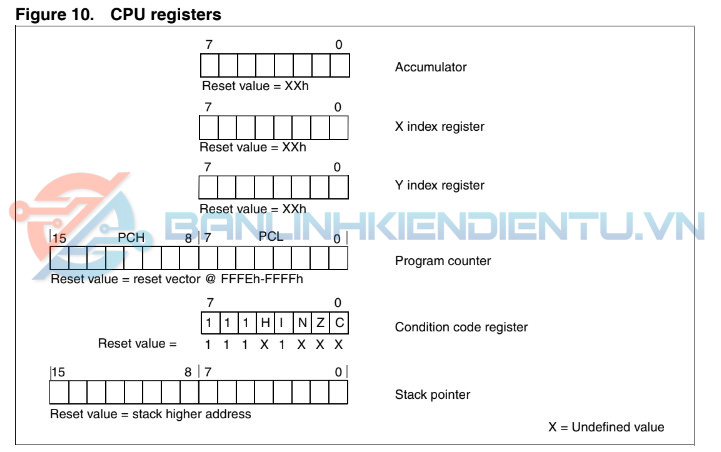

CPU này có kiến trúc 8 bit đầy đủ và chứa sáu thanh ghi bên trong cho phép xử lý dữ liệu 8 bit hiệu quả.

● 63 lệnh cơ bản

● Nhân 8 bit nhanh bằng 8 bit

● 17 chế độ địa chỉ chính

● Hai thanh ghi chỉ mục 8 bit

● Con trỏ ngăn xếp 16 bit

● Chế độ công suất thấp

● Ngắt phần cứng có thể che giấu

● Ngắt phần mềm không thể che giấu

Thanh ghi CPU

6 thanh ghi CPU được hiển thị trong Hình này không có trong ánh xạ bộ nhớ và được truy cập bằng các lệnh cụ thể.

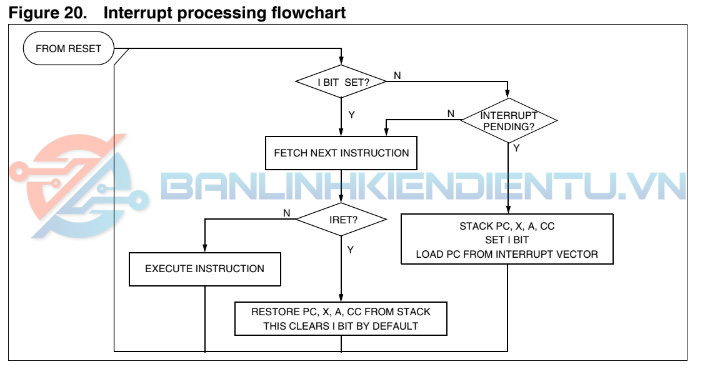

Ngắt

Lõi ST7 có thể bị ngắt bằng một trong hai phương pháp khác nhau: ngắt phần cứng có thể che dấu như được liệt kê trong Bảng ánh xạ ngắt và ngắt phần mềm không thể che dấu (TRAP). Sơ đồ luồng xử lý ngắt được hiển thị trong Hình này: Sơ đồ luồng xử lý ngắt.

Các cờ ngắt ngoại vi khác nhau trong thanh ghi trạng thái có thể gây ra ngắt khi chúng hoạt động nếu cả hai:

● Bit I của thanh ghi CC bị xóa.

● Bit cho phép tương ứng được đặt trong thanh ghi điều khiển.

Nếu bất kỳ điều kiện nào trong hai điều kiện này là sai, ngắt sẽ được chốt và do đó vẫn đang chờ xử lý.

Xóa yêu cầu ngắt được thực hiện bằng cách:

● ghi “0” vào bit tương ứng trong thanh ghi trạng thái hoặc

● truy cập vào thanh ghi trạng thái trong khi cờ được đặt theo sau là đọc hoặc ghi một thanh ghi liên quan.

Chế độ bảo vệ

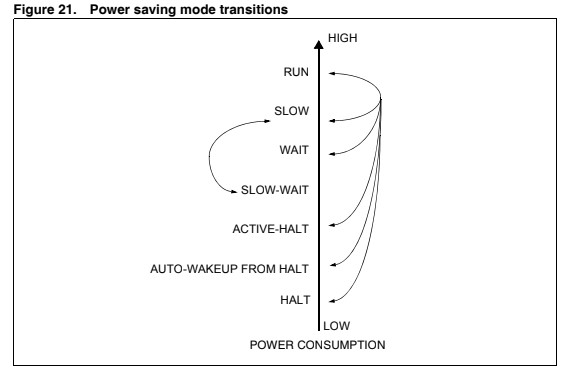

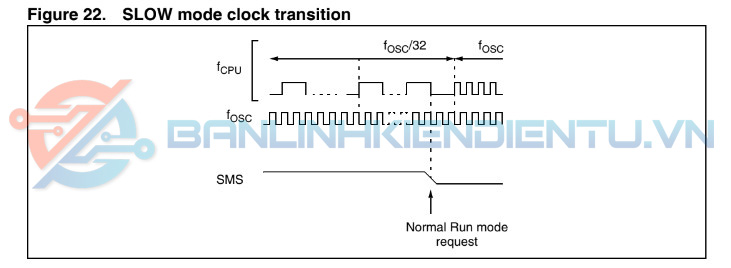

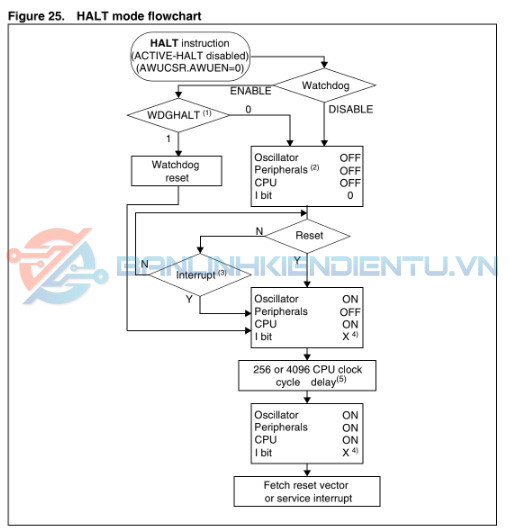

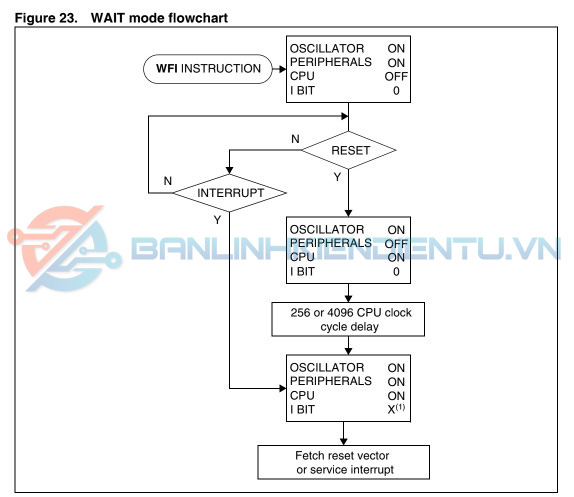

Để cung cấp một thước đo linh hoạt lớn cho ứng dụng về mặt tiêu thụ điện năng, năm chế độ tiết kiệm điện năng chính được triển khai trong ST7 (xem Hình này):

● Slow (chậm)

● Wait (and Slow-Wait) (chờ)

● Active Halt (dừng chủ động)

● Auto Wake up From Halt (AWUF) (tự động đánh thức trạng thái dừng)

● Halt (dừng)

Sau khi ĐẶT LẠI, chế độ hoạt động bình thường được chọn theo mặc định (Chế độ chạy). Chế độ này điều khiển thiết bị (CPU và thiết bị ngoại vi nhúng) bằng đồng hồ chính dựa trên tần số dao động chính chia hoặc nhân với 2 (fOSC2). Từ chế độ CHẠY, các chế độ tiết kiệm điện năng khác nhau có thể được chọn bằng cách đặt các bit thanh ghi có liên quan hoặc bằng cách gọi lệnh phần mềm ST7 cụ thể có hành động phụ thuộc vào trạng thái dao động.

Cổng I/0

Các cổng I/O cho phép truyền dữ liệu. Một cổng I/O có thể chứa tới 8 chân. Mỗi chân có thể được lập trình độc lập như một đầu vào kỹ thuật số hoặc đầu ra kỹ thuật số. Ngoài ra, các chân cụ thể có thể có một số chức năng khác. Các chức năng này có thể bao gồm ngắt ngoài, đầu vào/đầu ra tín hiệu thay thế cho các thiết bị ngoại vi trên chip hoặc đầu vào tương tự.

Một Data Register (DR) và một Data Direction Register (DDR) luôn được liên kết với mỗi cổng. Option Register (OR), cho phép các tùy chọn đầu vào/đầu ra, có thể được triển khai hoặc không. Mô tả sau đây sẽ tính đến thanh ghi OR. Một chân I/O được lập trình bằng các bit tương ứng trong các thanh ghi DDR, DR và OR: bit x tương ứng với chân x của cổng.

Lưu ý quan trọng

Kết quả chuyển đổi ADC không chính xác

Chuyển đổi không chính xác xảy ra với tỷ lệ thấp hơn 50 trên một triệu. Các chuyển đổi như vậy xảy ra khi điện áp đo được chỉ nằm giữa 2 giá trị số liên tiếp. Giải pháp thay thế Nên triển khai bộ lọc phần mềm để loại bỏ kết quả chuyển đổi không chính xác bất cứ khi nào chúng có thể gây ra hậu quả không mong muốn.

Độ chính xác của bộ chuyển đổi A/D cho lần chuyển đổi đầu tiên

Khi ADC được bật sau khi tắt nguồn (ví dụ khi thức dậy từ HALT, ACTIVE-HALT hoặc cài đặt bit ADON trong thanh ghi ADCCSR), độ chính xác của lần chuyển đổi đầu tiên (8 bit hoặc 10 bit) không đạt độ chính xác được chỉ định trong bảng dữ liệu.

Giải pháp thay thế

Để có độ chính xác được chỉ định trong bảng dữ liệu, phải bỏ qua lần chuyển đổi đầu tiên sau khi bật ADC.

Tác động của dòng điện âm lên độ chính xác của ADC

Việc đưa dòng điện âm vào chân đầu vào tương tự làm giảm đáng kể độ chính xác của Bộ chuyển đổi AD. Bất cứ khi nào cần thiết, nên ngăn chặn việc đưa dòng điện âm vào bằng cách thêm một diode Schottky giữa các I/O liên quan và đất. Việc đưa dòng điện âm vào chân đầu vào kỹ thuật số làm giảm độ chính xác của ADC, đặc biệt là nếu thực hiện trên chân gần kênh ADC đang sử dụng.

Xóa các ngắt đang hoạt động bên ngoài chương trình ngắt

Khi một yêu cầu ngắt đang hoạt động xảy ra cùng lúc với cờ hoặc mặt nạ ngắt liên quan đang được xóa, thanh ghi CC có thể bị hỏng.

Bối cảnh ngắt đồng thời

Triệu chứng không xảy ra khi các ngắt được xử lý bình thường, tức là khi:

● Yêu cầu ngắt được xóa (đặt lại cờ hoặc mặt nạ ngắt) trong chương trình ngắt của riêng nó.

● Yêu cầu ngắt được xóa (đặt lại cờ hoặc mặt nạ ngắt) trong bất kỳ chương trình ngắt nào.

● Yêu cầu ngắt được xóa (đặt lại cờ hoặc mặt nạ ngắt) trong bất kỳ phần nào của mã trong khi ngắt này bị vô hiệu hóa.

Nếu không đáp ứng các điều kiện này, có thể tránh triệu chứng bằng cách triển khai trình tự sau:

Thực hiện thao tác SIM và RIM trước và sau khi đặt lại yêu cầu ngắt đang hoạt động

Xem thêm những sản phẩm vi điều khiển khác tại đây

Chưa có đánh giá nào.