AT24C128 24C128N SOP-8

6,000₫

Mã sản phẩm : 24C128N

Loại linh kiện: IC

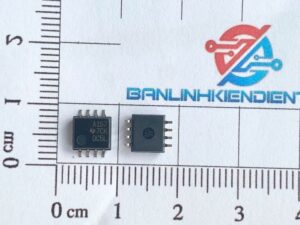

Kiểu chân: SOP-8

Hình thức : Mới

Tình trạng : Còn hàng

Hỗ trợ trực tuyến

Kinh doanh 1: 0333595662

Kinh doanh 2: 0973549046

(Giờ làm việc: 8h đến 18h từ T2-T7 )

Chú ý: Chỉ gửi đơn hàng tối thiểu 50.000 vnđ. Đơn hàng chưa bao gồm phí vận chuyển.

Kinh doanh 1: 0333595662

Kinh doanh 2: 0973549046

(Giờ làm việc: 8h đến 18h từ T2-T7 )

Chú ý: Chỉ gửi đơn hàng tối thiểu 50.000 vnđ. Đơn hàng chưa bao gồm phí vận chuyển.

Danh mục: IC, Linh kiện điện tử

Giới thiệu về IC AT24C128

AT24C128 cung cấp 131.072 bit bộ nhớ chỉ đọc có thể lập trình và xóa bằng điện nối tiếp (EEPROM) được tổ chức thành 16.384 từ, mỗi từ 8 bit. Tính năng xếp tầng của thiết bị cho phép tối đa 4 thiết bị chia sẻ một bus 2 dây chung. Thiết bị được tối ưu hóa để sử dụng trong nhiều ứng dụng công nghiệp và thương mại, nơi mà hoạt động điện áp thấp và công suất thấp là điều cần thiết. Các thiết bị có sẵn trong các gói JEDEC PDIP 8 chân, EIAJ 8 chân, JEDEC SOIC 8 chân, TSSOP 14 chân và LAP 8 chân tiết kiệm không gian. Ngoài ra, toàn bộ họ sản phẩm có sẵn trong các phiên bản 5.0V (4.5V đến 5.5V), 2.7V (2.7V đến 5.5V) và 1.8V (1.8V đến 3.6V).

Đặc trưng kỹ thuật

- Hoạt động điện áp thấp và điện áp tiêu chuẩn:

– 5.0 (VCC = 4.5V đến 5.5V)

– 2.7 (VCC = 2.7V đến 5.5V)

– 1.8 (VCC = 1.8V đến 3.6V) - Được tổ chức bên trong 16.384 x 8 và 32.768 x 8

- Giao diện nối tiếp 2 dây

- Schmitt Trigger, Đầu vào được lọc để loại bỏ tiếng ồn

- Giao thức truyền dữ liệu hai chiều

- Khả năng tương thích 1 MHz (5V), 400 kHz (2.7V) và 100 kHz (1.8V)

- Ghim bảo vệ ghi để bảo vệ dữ liệu phần cứng và phần mềm

- Chế độ ghi trang 64 byte (Cho phép ghi trang một phần)

- Chu kỳ ghi tự định thời gian (thông thường là 5 ms)

- Độ tin cậy cao

– Độ bền: 100.000 chu kỳ ghi

– Lưu giữ dữ liệu: 40 năm

– Bảo vệ ESD: > 4000V - Thiết bị cấp độ ô tô và nhiệt độ mở rộng có sẵn

- JEDEC PDIP 8 chân, JEDEC và EIAJ SOIC 8 chân, TSSOP 14 chân và các gói mảng không chì 8 chân

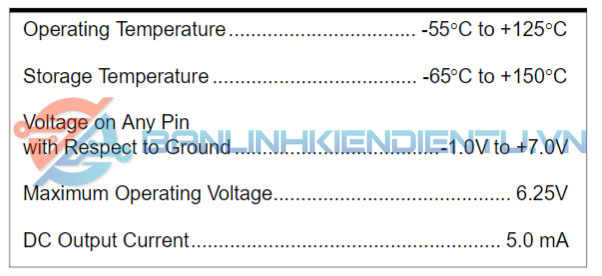

Thông số kỹ thuật

Sơ đồ khối chức năng

Sơ đồ chân

Kích thước IC AT24C128

Xem thêm: Nhiều sản phẩm IC nguồn khác

Datasheet AT24C128

Hãy là người đầu tiên nhận xét “AT24C128 24C128N SOP-8” Hủy

Sản phẩm tương tự

38,000₫

120,000₫

16,500₫

17,000₫

Chưa có đánh giá nào.